AMD Zen5搭載のStrix Point APUと見られるCPU-Z情報などが登場。L3キャッシュはZen 2以来の分割構成に戻る。

AMDでは2024年以降にZen5アーキテクチャーを採用したRyzen 8000シリーズCPUの投入を予定しています。このRyzen 8000シリーズにはデスクトップ向けのGranite RidgeとノートPC向けのStrix系(Strix PointとStrix Halo)が用意されていますが、今回この中でStrix PointのCPU-Z情報などが登場し、コア構成とキャッシュ容量や構成に関する情報が明らかになりました。

AMD Zen 5 “Strix” APU – Performancedatabases.com

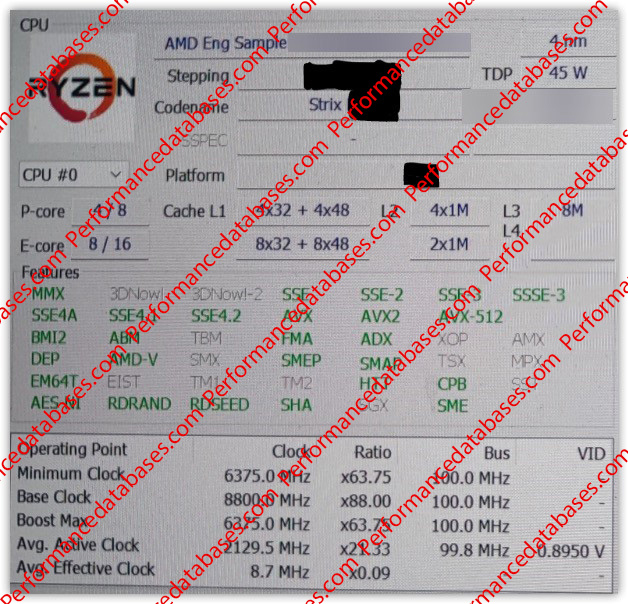

Strix Point APUについてはIntelのAlder Lakeから採用されている高性能コアと高効率コアで構成されたハイブリッドアーキテクチャーが採用されると見られています。過去のリークではStrix Pointについては高性能コアであるZen5を合計4コア、高効率コアであるZen5cを8コア搭載する4P+8E構成の合計12コア24スレッドが最大構成になると見られていました。

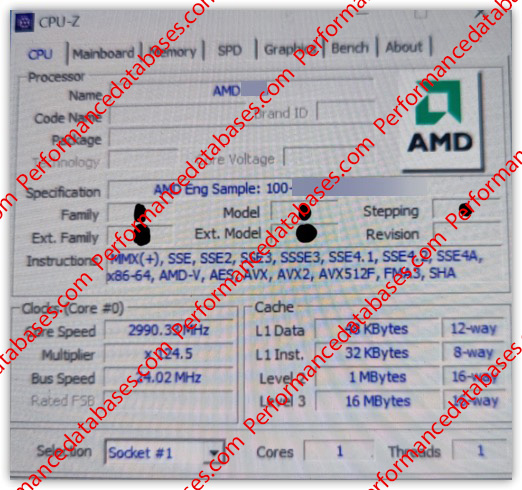

今回、Performancedatabasesが入手したStrix PointのCPU-ZおよびHWiNFOの情報から上述のリークと同じ4P+8E構成であることが明らかになっていますが併せてキャッシュ構成についても明らかになりました。

キャッシュ構成としては、L2キャッシュはP-Core側では各コア1MBで合計4MB、E-Core側では4コア毎に1MB、8コアで合計2MBのキャッシュ容量を共有するという構成になっています。一方で、L3キャッシュについてはP-CoreとE-Coreでそれぞれ8MBを備えているという構成になるようです。

先代Zen 4のアーキテクチャーではL2キャッシュは各コア1MBでノートPC向けではL3キャッシュは全コア共有で16MBが備わっていました。Zen 4cについてもL2キャッシュは各コア1MBとなっていましたが、Zen5cにおいては各コアのL2キャッシュ容量は8E構成の場合は各コアにつき512KBの容量に半減しています。このL2キャッシュ容量縮小についてはAPUと言う限られた面積に搭載するために行われた対応と考えられています。

AMD Zen5のキャッシュ構成が判明。L3は分割構成に戻り、L2は最大3MBに

L3キャッシュについてもZen 4では全コア共有で16MBが使えていましたが、Strix PointではP-CoreとE-Coreそれぞれで8MBとなっており、2つのCPU間ではキャッシュ容量の共有は性能の大幅低下無しには行えません。このL3キャッシュ構成はZen 4やZen 3と言うよりZen 2に戻っているようにも見受けられるのですが、全コアでキャッシュ容量を共有するにはリングバスと呼ばれる環状線状の回路が用意されており、コア数が増えるほど性能が低下する弱点を持っています。そのため、Zen5ではア間の通信はハシゴ状のバスで接続する事でコア間の通信ボトルネックをリングバスに比べて大幅な削減を行うとともに、Zen 2世代などで問題となっていたキャッシュ跨ぎによる性能低下も抑えられると見られています。

コメント