AMD Strix Haloには低電力なZen 5 LPコアをI/Oダイに内蔵。ダイのレンダー画像と仕様に関する情報が登場

AMDは2024年にZen 5とRDNA3+を組み合わせたAPUのStrix Pointを投入予定ですが、この上位APUでCPUとGPUコア数を増やし、性能を大幅強化したStrix Haloが2025年初頭に投入されると言われています。今回、Strix Haloのダイのレンダー画像が登場するとともに、各ダイの仕様などの情報が登場しました。

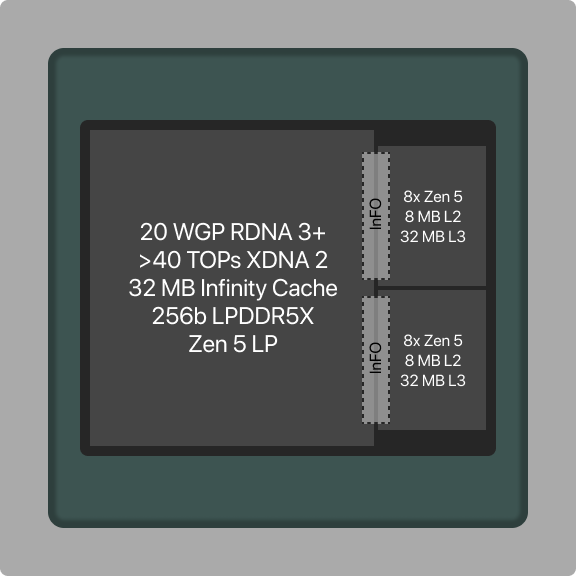

Strix Haloはチップレット構造になることは過去のリークでも明らかにされていますが、リーカーのOlrak_29氏によるとStrix Halは合計3つのダイで構成され、1つの大きなダイはI/OダイとなりGPUやNPUを内蔵、2つの小さなダイはZen 5を8コア内蔵するCCDになります。また、CPUとI/Oダイ含めてRadeon RX 7900のGPUで用いられているInFOパッケージング技術を活用して製造されるとのことです。

I/Oダイ側には最大40コアのRDNA3+アーキテクチャーで構成されるCompute Unitと32MBのInfinity Cache、256-bitのLPDDR5Xメモリーコントローラー、そして性能が40 TOPsのXDNA2が備わります。この辺りの情報は過去のリークでも登場していますが今回このI/OダイにZen 5 LPと言うコアも内蔵されるようです。

このZen 5 LPは過去のリークには無かった情報ですが、Strix Haloは55~130Wで動作するAPUですが、ターゲットはノートPCであるためバッテリー持続時間も重要となります。そのため、AMDではI/Oダイに省電力で動作するZen 5 LPコアを内蔵することで、低負荷時はCCDを停止させることで消費電力を下げようとしているようです。

これはIntelのMeteor Lakeで採用されているLPE-Coreとほとんど同じで、Meteor LakeもGPUとNPUなどを備えるSoCダイに省電力なLPE-Coreを内蔵し、低負荷時はP-CoreとE-Coreは停止する仕組みになっています。

AMDのStrix HaloならびにStrix PointなどのZen 5アーキテクチャーを備えるAPUは2024年6月初旬に開催されるComputex 2024にてラインアップや詳細が発表されるとみられています。

AMDのStrix Haloではチップレット構造が採用されるほか、パッケージング技術はRadeon RX 7900搭載のNavi 31に似ているとも過去のリークで言われていましたが、あとは大きさがどの程度かが気になるところです。

I/OダイにはZen 5 LPと言われる低電力コアが内蔵されるようですが、恐らくZen 5cベースのCPUになると考えられます。そのため、1コアでも2スレッド、2コアなら4スレッドでの動作が可能で、ブラウジングや動画のストリーミングなど軽い作業はZen 5 LPのみの動作でこと足りてしまうかもしれません。

ただ、Strix Haloは最大40コアのGPU、256-bitのLPDDR5Xコントローラー、32MBのInfinity Cacheに加え、16コアのZen 5とZen 5 LPコアなど全部入りAPUでもあるためどのような価格になるのかが非常に気になるところです。

Olrak29_ | X (Twitter)