Intelでは2023年にAlder Lakeに搭載されているP-Coreで構成されたSapphire Rapids Xeonを投入しましたが、AMDのEPYC Genoaに対抗するためにRaptor Lakeに搭載されているP-Coreで構成されたEmerald Rapids Xeonを2023年末に投入予定です。今回、このEmerald Rapidsの詳細情報をSemiAnalysisが入手と解析を行い、コア数やキャッシュ容量などが明らかになりました。

Intel 第5世代Xeon Emerald Rapidsでは最大64コア構成でEPYC Genoa並のキャッシュ容量に。一方でダイサイズが大型化しコストは高騰へ

Intelでは近年、サーバー・データーセンター向けCPUにおいてAMDのEPYCシリーズにシェアを奪われており、2023年末までにはAMDのシェアは30%以上に達する可能性も出ています。一方でこのサーバー・データーセンター向けCPUは収益率が高くIntelもAMDの躍進を止める必要性があります。

そのため、Intelでは2023年に当初計画から2年遅れでAlder Lakeに搭載されているP-Core、Golden Coveで構成されたSapphire Rapids世代のXeonを投入しました。しかし、AMDでは同時期にZen 4アーキテクチャーで構成された最大96コアのEPYC Genoaを投入しましたが、IntelもこのEPYC Genoaに対抗するために最新鋭のRaptor Lakeに搭載されているRaptor Coveで構成されたEmerald Rapidsを2023年末に投入を予定しています。今回、このEmerald Rapidsについて半導体関係の解析などを行うSemiAnalysisにて詳細情報と出現している情報をもとにコア数やキャッシュ容量、コスト面での競争力が明らかにされています。

Intel Emerald Rapids Backtracks on Chiplets – Design, Performance & Cost | Semianalysis

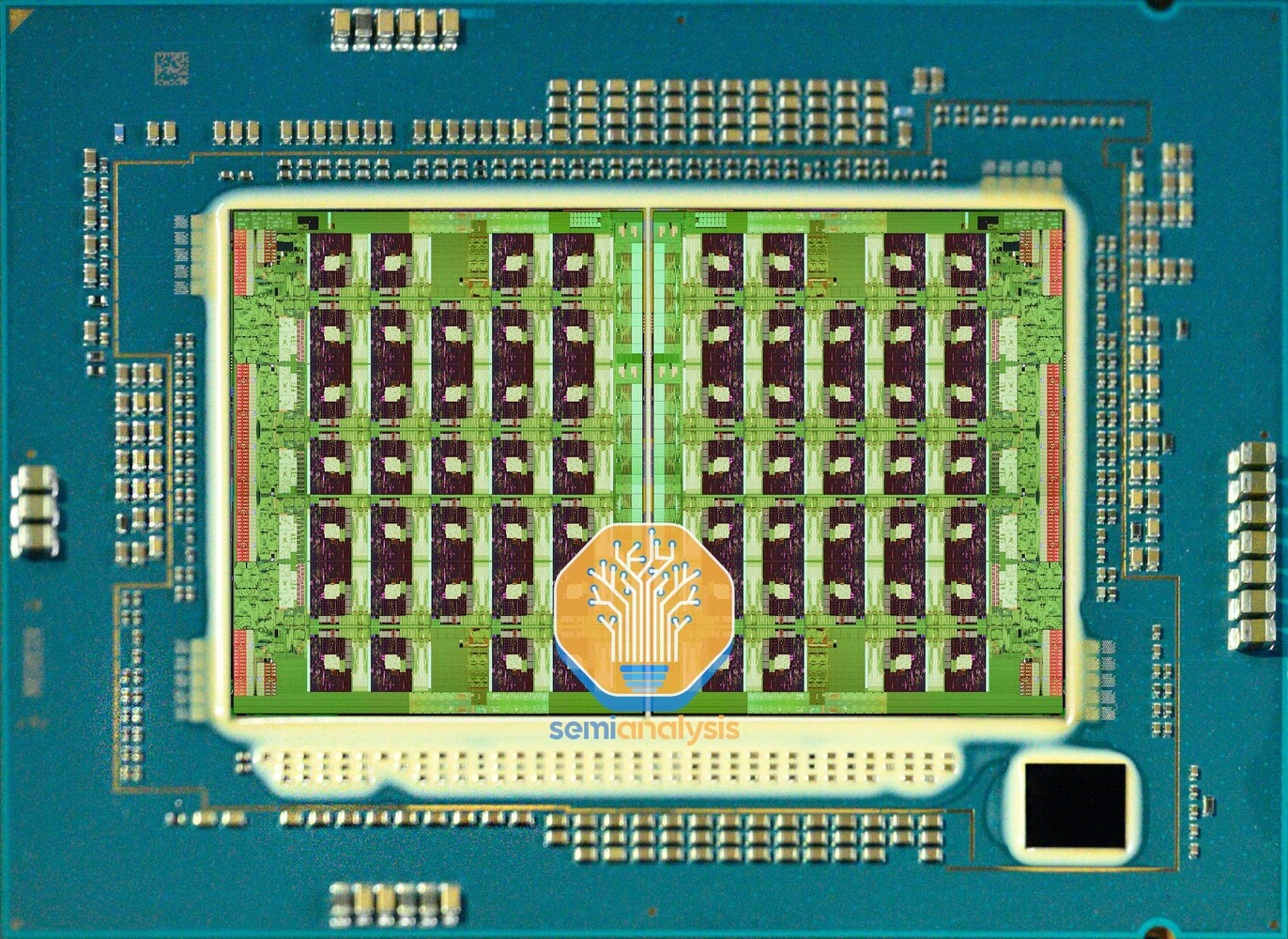

IntelのSapphire Rapidsでは4つのチップレットで構成されたMulti Chip Module (MCM)構造が採用されていますが、Emerald Rapidsではこのチップレットが最大2つにまとめられています。

各チップレットにはRaptor Coveアーキテクチャーを採用したCPUコアが合計33コア搭載されています。このコアの内1コアは歩留まり向上のために予備として置かれる予定で、Emerald Rapidsとしては最大64コア構成となります。また、前世代のSapphire Rapidsで搭載されていたGolden Coveに対して5~10%のIPC向上が見込まれているため、最上位モデルのEmerald Rapidsに関してはSapphire Rapidsに比べて性能は比較的大きく向上すると見られています。

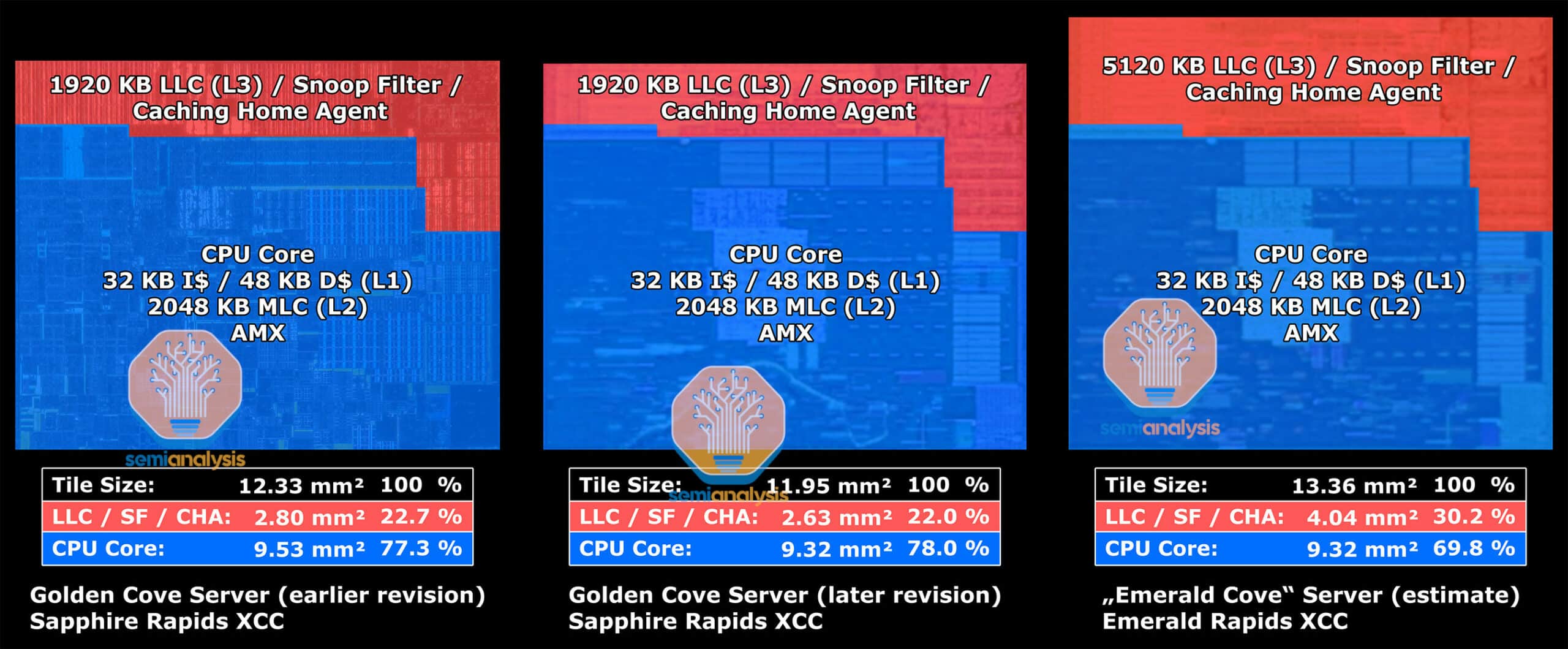

キャッシュ面では各コアにL2キャッシュが2MB、L3キャッシュは5MBが搭載されており、CPU全体ではL2キャッシュが128MB、L3キャッシュが320MBで合計448MBのキャッシュ容量を持つことになります。

このキャッシュ容量は同じく64コアのEPYC Genoaの96MBのL2と320MBのL3の合計、480MBに迫る容量となっています。

IntelのRaptor LakeではAMDのZen 4に対してほぼ同等のCPU性能を持っており、キャッシュ容量も同じコア数のEPYC Genoa並ということで性能面では同等レベルに位置すると見られています。しかし、コア数の増加やキャッシュ容量の増加に伴い、各チップレットのダイサイズは大型化する傾向にあり、コスト上昇要因になる可能性があるようです。

Sapphire Rapidsに搭載ではチップレットが合計4つあったことから、接続インターフェイス類にチップレット面積の一部が専有されていましたが、チップレットを2つにまとめることで接続インターフェイス類を追加のコア面積に割り当てることが可能になっています。しかし、各コアに搭載されているキャッシュ容量の増加に伴い各コアの面積は増加傾向にあり、Sapphire Rapidsの全体ダイ面積の1510mm2に対して、Emerald Rapidsでは1493mm2とほとんど変わらない面積になっています。これだけで見ればコスト増加要因はありませんが、接続インターフェイスが減らされることで冗長性が少なくなるためIntelのIntel 7プロセスの歩留まり次第ではコストを大きく跳ね上げる原因になり得るようです。

そのため、歩留まりがIntelの想定を下回ることになれば、コスト競争力の面ではAMDのEPYC Genoaや、キャッシュ容量が大きく増やされたEPYC Genoa-Xに対して劣る可能性も出てくる可能性があるようです。

ただし、IntelのEmeralds Rapidsに関しては2017年から実用化されているIntel 7 (10nm)プロセスが採用されており相当、熟成されたプロセス担っています。そのため、Intelがこのような変更を加えるからには歩留まりの面で相当自身を持っているとも考えられます。