TSMCでは2023年から3nmプロセスの量産化を行うと見られていますが3nmについては製造単価が非常に高価な事に加え、TSMCでは2020年初期に比べると30%近い値上げを繰り返してきた事からAMDやNVIDIAなど主要な顧客が離れて行っているようです。しかし、この状況に危機感を覚えたのか3nmプロセスの値下げを検討しているようです。

TSMCが3nmチップの製造価格値下げ検討中。AMDやNVIDIAに3nmプロセスが売れないため。

TSMC Might Cut 3nm Prices to Lure AMD, Nvidia | Tom's Hardware

TSMCの3nmについては従来の5nmに比べて面積辺りの密度の高いチップを実現できる事からパフォーマンスや電力効率の向上など多くの利点をもたらしますが、TSMC 3nmの初期バージョンであるN3Bについては非常に高いコストがかかると言われています。

このN3Bでは最大25層の極端紫外線(EUV)露光を行う事で高密度な回路を実現すると見られていますが、このEUV露光を行う機械は1台辺り200億円以上し、25層露光するとなると最低25台、5000億円近いコストが製造設備だけでかかると見られています。

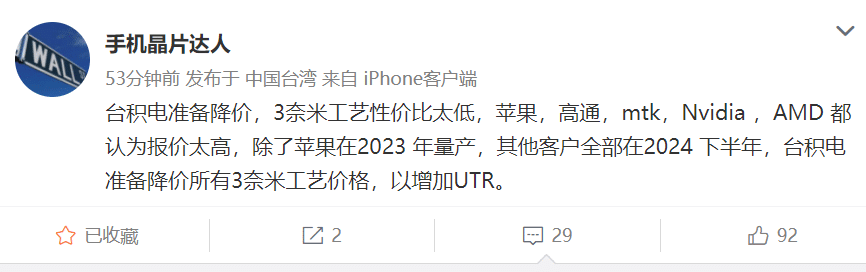

そのため、TSMCではN3Bウェハー1枚あたり$2.0万とN5ウェハーのコスト、$1.6万の1.25倍以上の製造コストがかかると言われています。そのため、このN3Bプロセスを採用するのはAppleだけという状況となっています。

ただ、TSMCではこの高いコストを下げるためにコストを抑えたN3Eというプロセスも開発していますが、AMDやNVIDIA、Qualcommといった大口顧客を繋ぎ止めるためこの廉価版3nmプロセスであるN3Eについて値下げを検討しているようです。

リーク情報によると、TSMCではN3BやN3Eなど3nmプロセス全般についてAMDやNVIDIA、Qualcommなど主要顧客を引き留めるために全体的な値下げを検討しているとのことです。

TSMC製のCPUやGPUを扱うAMDについては最新鋭のZen 4やRDNA 3についてはTSMC 5nmを利用し、TSMC 3nmを使うのは2024年以降に登場するZen5やRDNA 4からとなっています。ただ、AMDについてはチップレットデザインを採用する中で可能な限り先端プロセスの使用量を減らすためにRDNA 3では一部を6nm化しており、この流れはZen5やRDNA 4でも続くと考えられています。

また、NVIDIAもTSMC 3nmを次世代グラフィックスカードのBlackwellアーキテクチャーで採用すると言われていますがこちらも一部のハイエンドのみで3nmを採用し、コスト条件が厳しいミドルレンジクラスでは4nmなどを採用する可能性も考えられています。

TSMCの3nmプロセスについてはAppleが採用するN3Bの他、値下げが検討されているN3EなどではSRAM密度の向上が行われておらず、最近のCPUやGPUでトレンドとなっている大容量キャッシュを搭載すると先端プロセスを採用する利点の1つでもあるダイサイズ縮小が困難となります。そのため、TSMCとしてはこのディスアドバンテージも鑑みて値下げの検討をしているとも考えられます。