AMD Strix Halo APUの詳細仕様が判明。TDPは最大120WでStrix Pointの2倍のダイサイズに

AMDは2025年に最大16コアのZen 5とRDNA 3.5で構成されるCompute Unitを最大40コア搭載した高性能APU「Strix Halo」を投入予定です。このStrix Haloを搭載するASUSのタブレット「ASUS ROG Flow Z13」の設計段階での検討資料と見られる情報がリークし、Strix Haloのダイの模式図やダイサイズ、TDPなどの一部仕様が明らかになりました。

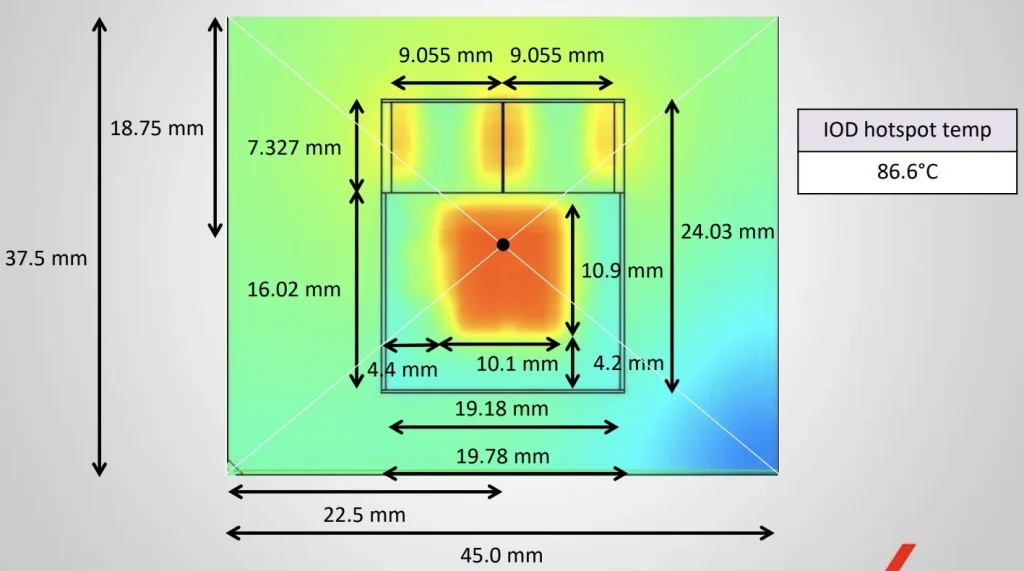

Strix HaloはノートPC向けに初めてチップレット構造を取り入れるAPUで、合計3つのチップレットで構成されています。画像の上部にある2つのダイはそれぞれ8コアを内蔵するCCDで、合計16コアのZen 5を内蔵しています。このダイは66.345mm²で、デスクトップ向けZen 5のCCDとほとんど同じサイズです。その下にある巨大ダイがRDNA 3.5 GPUとI/O関連を収めたI/Oダイで、ダイサイズは307.26mm²と非常に大きく、GeForce RTX 4070に採用されているAD104 GPUよりも大きく、Radeon RX 7800 XTに採用されているNavi 32 GPUより小さいサイズです。

このStrix HaloのI/OダイにはRDNA 3.5で構成されるCompute Unitが合計40コア搭載されており、最も発熱が大きい部分です。

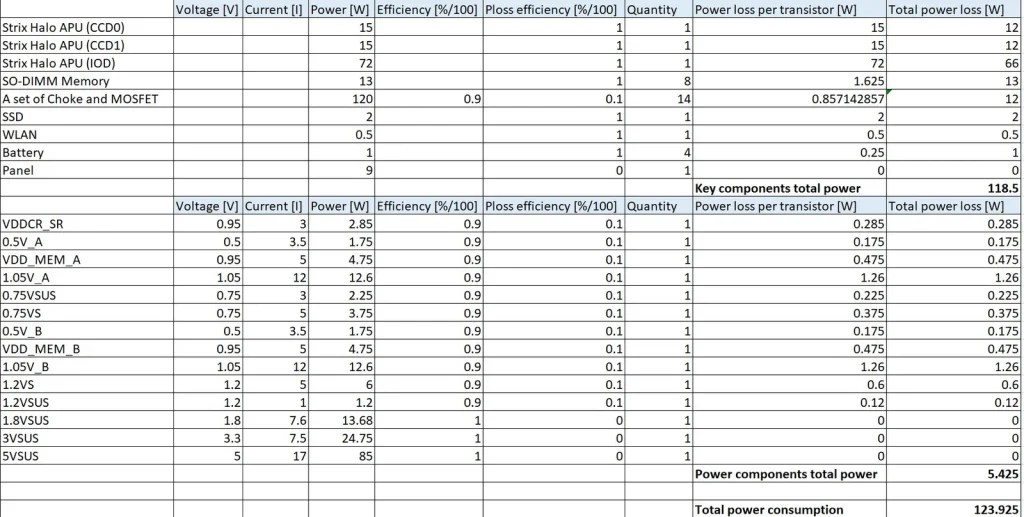

消費電力に関しては、各パーツごとに示されており、CCDは1基あたり15Wで2基で30W、GPUを内蔵するI/Oダイは最大72Wの消費電力が計画されています。また、このAPUはオンボードに加え、SO-DIMM構成もサポートしており、メモリー関連は最大13Wの消費電力です。

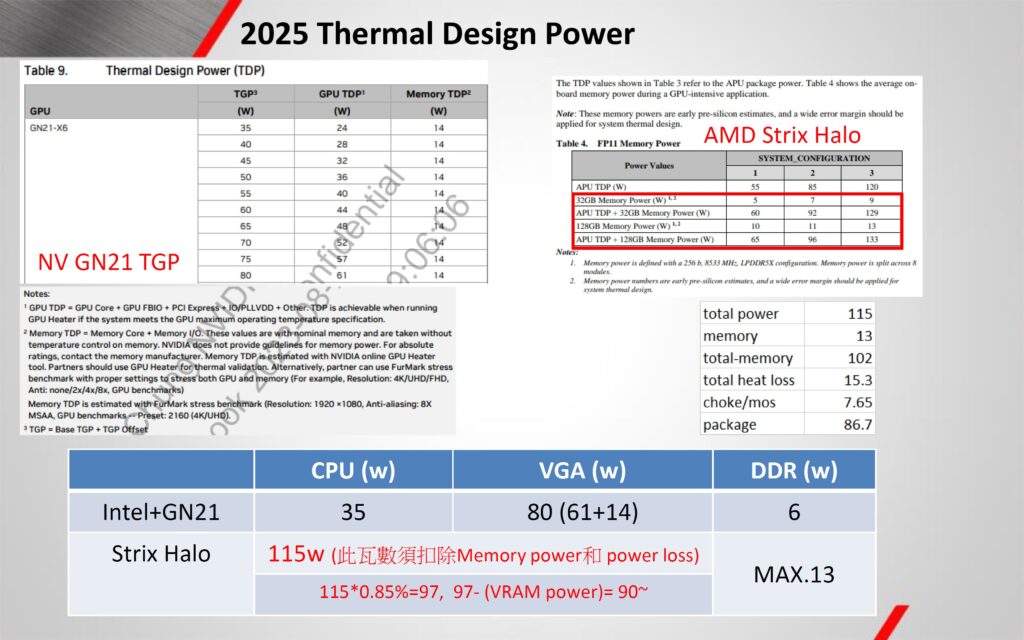

Strix Halo APUには合計3つのTDP区分が設けられており、最上位モデルはAPU全体でTDPが120W、その下のモデルが85W、最小の消費電力で動くモデルが55Wです。メモリーは256-bitのバス幅を実現するために32GBか128GBの2つの構成があり、メモリー仕様はLPDDR5X-8533 MHzが採用されます。

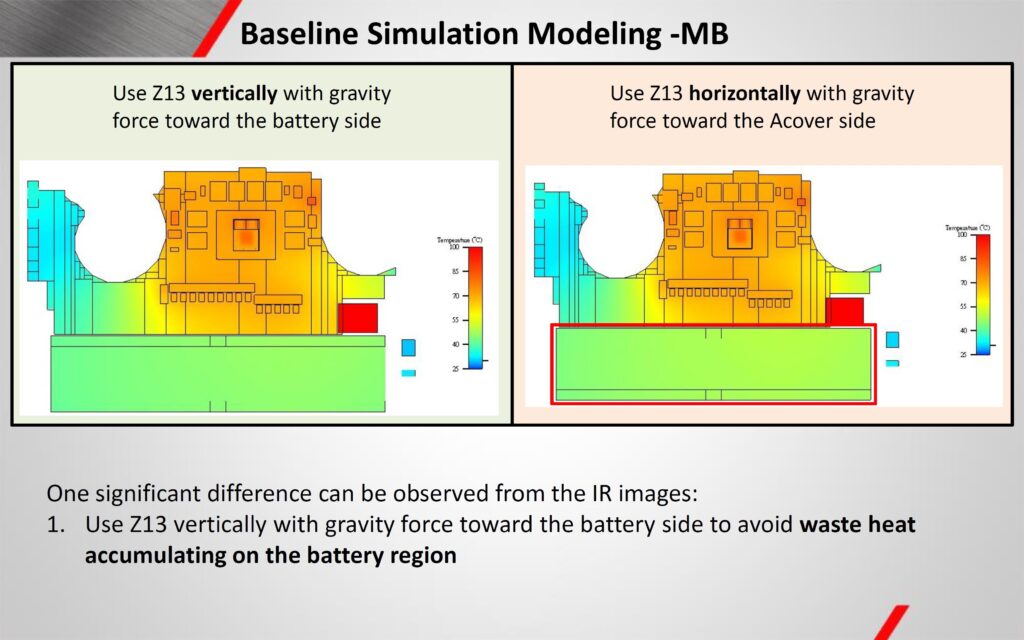

ASUS ROG Flow Z13のマザーボードを示した資料では、Strix APUの周りに8枚のメモリーモジュールが配置されており、グラフィックスカードのようなレイアウトになっています。このオンボードの場合、256-bitのバス幅を実現し、内蔵GPUの最大のボトルネックであるメモリー帯域幅を大幅に改善してパフォーマンスを向上させます。

Strix Haloは2025年1月に開催されるCES 2025で正式発表が行われると見られており、主にハイエンドなゲーミングノートPCなどへの搭載が想定されています。

AMDのStrix Haloは非常に高いグラフィックス性能を備えたAPUとして期待が高まっています。LPDDR5XをAPUを囲むように配置するなど、見た目はディスクリートGPUのようです。Strix Haloは最大120WのTDPを持つため、省電力性能も優れています。

通常、ノートPCでは35W程度のCPUとディスクリートGPUを搭載する必要がありますが、Strix Haloの最上位モデルはそれを一体化し、同等性能を持つGeForce RTX 4060(115W)と比較しても優れた省電力性を実現しています。そのため、Strix Haloが今後のゲーミングノートPCのメインストリームになる可能性が高く、非常に期待されています。

Sam Jiun-Wei Hu