ここ最近、AMDの次期GPUアーキテクチャであるRDNA3に関するリークが多く出現していますが、そのリークについて7月時点での情報を3DCenter.orgがまとめてくれました。

多くのリークを基にNavi31の仕様をまとめ

7月下旬ごろから様々なリーカーからAMDの次期GPUアーキテクチャーであるRDNA3を採用するNavi31の情報が出現していますが、断片的で追うのは大変です。そこで、これまでに出現した情報を分かりやすくまとめてくれた方がいるので紹介しようと思います。

Navi31にはGPUダイが2つとキャッシュ用ダイが1つ搭載に

AMD Navi 31 specs, based on leaks/rumors by @greymon55 @KittyYYuko @kopite7kimi & Bondrewd

TSMC 5nm (MCD 6nm)

MCM: 2 GCD + 1 MCD

6 SE (3/GCD)

60 WGP (30/GCD)

no more CUs

15360 FP32

larger Infinity Cache

256 Bit GDDR6

tape-out soon

release expected H2/2022

perf target: N21 x2.5— 3DCenter.org (@3DCenter_org) July 26, 2021

3DCenterが過去にTwitter発のリーカーである@greymon55氏、@KittyYYuko氏、@kopite7kimi氏とBeyond3D上の掲示板に出現したユーザー、Bondrewd氏の情報が基となっています。

7月23日:AMD RDNA3 Navi31が間もなくテープアウト。仕様も一部判明

7月27日:RDNA3ではコアブロックがCompute UnitからWGPに替わる模様

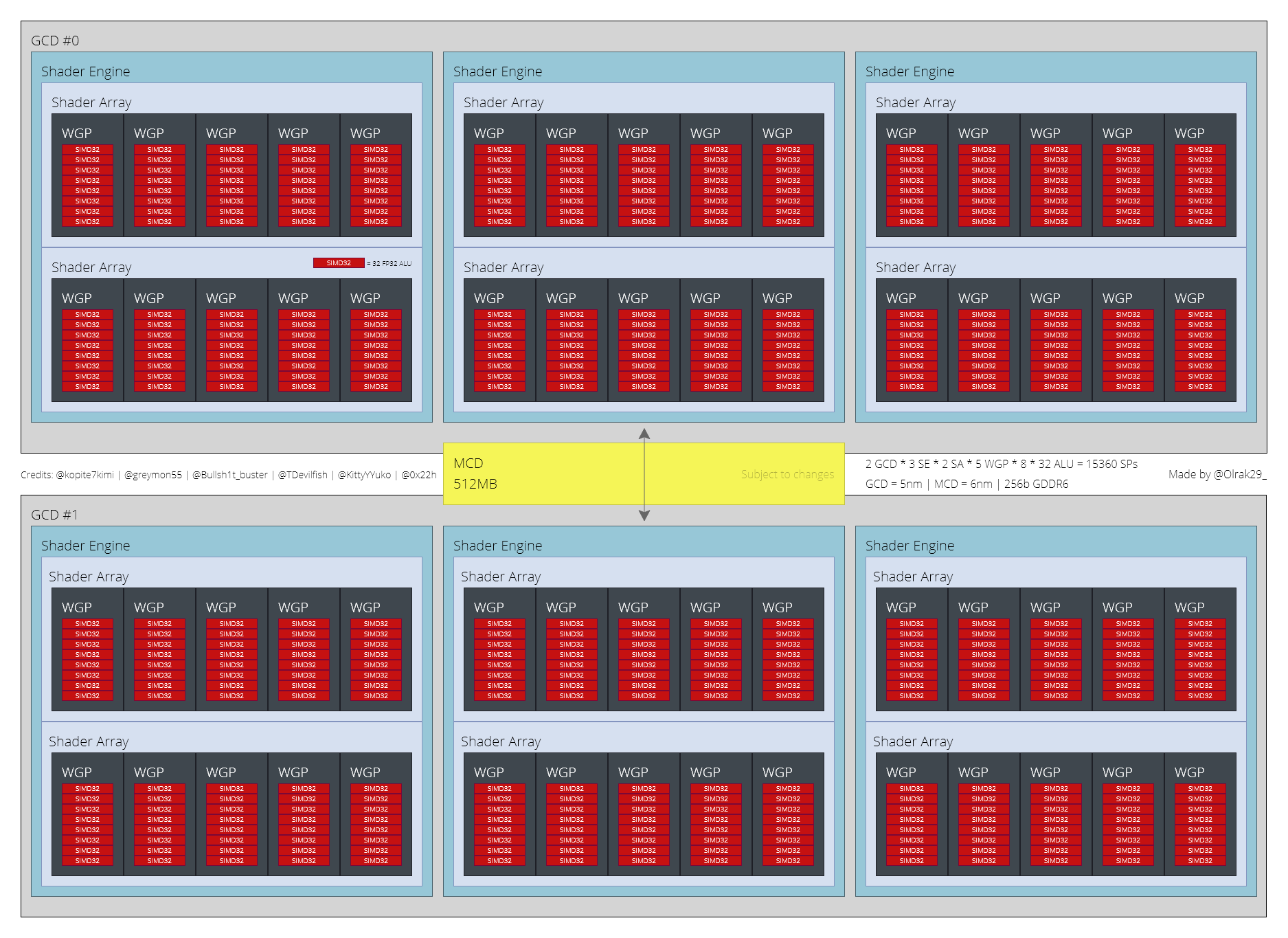

Navi31のGPUダイであるGraphics Core Die(GCD)が2つ搭載されており、これらは1つのMulti Cache Dieと呼ばれるキャッシュ専用ダイに繋がれるとの事です。乱暴にRyzen CPUを例に挙げて言うと、GCDがCPUダイに当たるCCD、MCDがI/Oダイと言ったところでしょうか。

このうち、GCDについてはTSMCの5nmプロセスが採用されます。こちらはN5なのかN5Pを採用するかは未定となっていますが、TSMC 5nmである事はほぼ確定のようです。一方で、MCDについてはTSMC 6nmが採用されるようです。

各GCDには3つのシェーダーエンジン(SE)が搭載され、各SEの中にはそのには2つのシェーダーアレー(SA)が搭載されるとの事です。さらに、このシェーダーアレーの中には5つのWGPが搭載され、各WGPの中には8つのSIMD32演算器と32のALU演算器が含まれているとの事です。

そのため、コア数としては2GCD x 3SE x 2SA x 5WGP x 8SIMD x 32ALU = 15360コアと言う数字になるようです。

※何個WGPの中にSIMD32が何個あるのかなどは@Olrak29_氏が作ったブロックダイアグラムが参考になります。

また、2つのGCDに接続されたMCDにはInfinity Cacheが搭載されると見られており、このInfinity Cache容量は最大で512MBになると言われています。一方で、このInfinity Cacheが大容量化される事からメモリーバス幅は控えめな256bitに設定される見込みになっています。この256bitは現行のRadeon RX 6900 XTやRX 6800 XTなどと同等となります。

なおパフォーマンス目標はNavi21に対して約2.5倍になっており性能面ではNVIDIAに挑もうとしているように見受けられます。

Navi31に関してはまだテープアウトもされていませんが、GPUとしては全く新しいMCMを採用していたり、NVIDIAに対して性能面で勝とうとしているなど高い関心が持たれる話題になっています。そのため、数多くのリークが出現するのだと思うのですが、この調子だとテープアウト後は更にリークが連発すると考えられますので定期的にNavi31に関する話が今後出ると考えられます。

少し気になるのが、半導体業界は秘匿性が高いイメージなのですが、それは製造技術面だけであって、製品に関してはこれぐらいガバガバなモノなのでしょうか・・・

コメント