AMDでは2024年頃を目途に大部分の設計を刷新するZen5アーキテクチャーを搭載するRyzen 8000シリーズやEPYC Turinを投入予定ですが、今回このZen5アーキテクチャーのキャッシュ周りに関するリーク情報が登場しました。

AMD Zen5アーキテクチャーではキャッシュ周りが刷新。L3は16MBx2変わるなどZen 2似の設計に、L2は最大3MBに大容量化しIPCが最大7%向上。

AMDでは2024年上半期を目途に次世代CPUアーキテクチャーであるZen5を採用するCPUの発売を計画しています。このZen5はTSMC 4nmまたは3nmなどの最先端プロセスを採用する他、アーキテクチャー面では「初代Zen並のアーキテクチャー刷新規模」とし、IPCはZen 4比で15~25%の大幅向上が計画されていますが、今回このZen5について初期プロトタイプで明らかになっている仕様などのリーク情報がAdoredTVから登場しています。

Zen 5 Secrets Revealed - it's Gonna Be (Really) Good - YouTube

AdoredTVによると、Zen5アーキテクチャーでは「初代Zen並のアーキテクチャー刷新規模」と言われる通り大規模な刷新が行われており、その一つがキャッシュ周りになるとのことです。

L3キャッシュについてはハシゴ状の共有キャッシュの使用です。以前のZenアーキテクチャーでは最大8コアのCCD内に4コア搭載するCCXが2つ内蔵されており、L3キャッシュはこのCCX毎に16MB持っていました。この構造の最大の弱点は各CCX内に存在する16MBのキャッシュにしかアクセスが出来ず、大容量なキャッシュが必要となる状況ではパフォーマンスが大きく低下する弱点がありました。

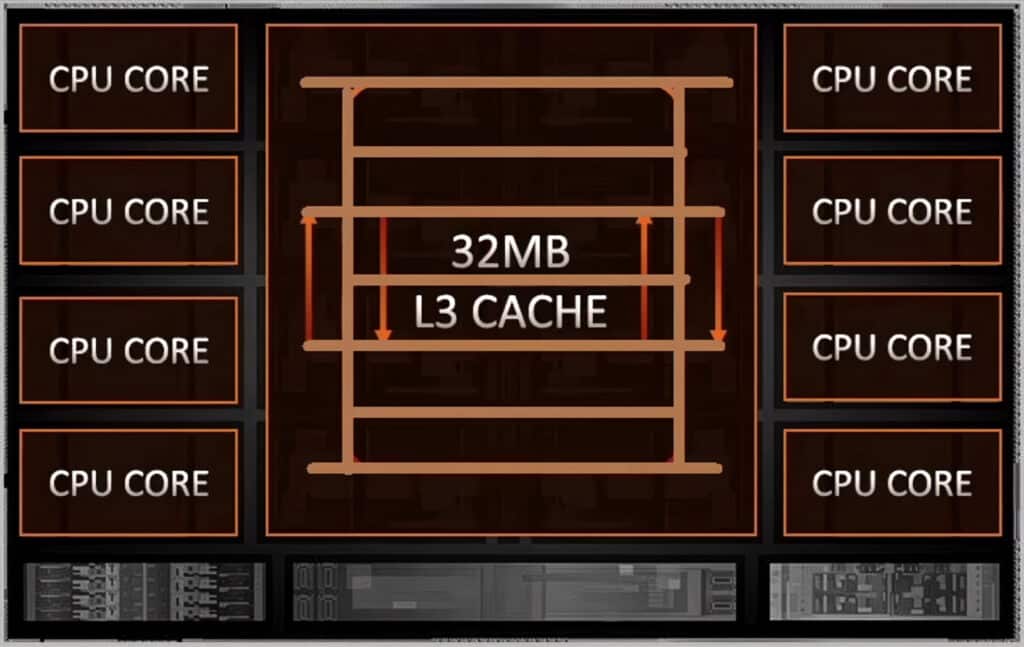

そのため、Zen 3ではCCXを排して、8コアが内蔵されたCCDの中には全コアが使える共有の32MBのL3キャッシュが搭載され、Zen 4でも同様の設計が引き継がれています。

しかし、Zen5ではこのキャッシュ構造が再び16MB毎に分かれた構造になるようです。この変更が加えられる背景としては、Zen 3から導入された全コア共有可能なL3キャッシュはリングバスと呼ばれる環状線状の通信回路が用意されているのですが、コア数が増えるとレイテンシーが増す弱点があります。(簡単に言うと、大阪環状線の停車駅が増える感じです。)

一方で、Zen5では16MB毎のキャッシュを2つ用意する一方で、コア間の通信はハシゴ状のバスで接続する事でコア間の通信ボトルネックをリングバスに比べて大幅な削減が可能となるようです。また、Zen5cなどで行われる多コア化を行ってもレイテンシーの増加が見られないというメリットもあるようです。なお、Zen5でL3キャッシュが合計32MB(16MBx2)に据え置かれると見られていますが、増やされる可能性もあるようです。

L2キャッシュについては現行のZen 4では各コアが1MBの容量を持っていますが、Zen5からは各コア毎に最低2MB、最大3MBのL2キャッシュ容量を持つように変更されるようです。このL2キャッシュ容量の増加に伴い、Zen 4に対してIPCは向上するようで、2MBの場合はマルチスレッド時で4%、3MBの場合は7%も向上が期待できるとのことです。ただ、これはマルチスレッド時限定で、シングルスレッドのワークロードでは1%程度の向上代しか無いとの事です。

なお、キャッシュが増える事によるレイテンシーの増加は現時点では確認されていないとの事です。

AMDのZenシリーズでは現行のCCD1基あたり8コアと言う構成は長らく変わっていませんが、Zen5ではコア数重視のZen5cや将来的なZen 6などを見越してL3キャッシュをリングバスから別の形に置き換えるものと見られています。また、L2キャッシュについては純粋なIPC向上に効果が見いだせることから大容量化が行われるようです。

L3キャッシュが分割化された場合、Zen 2などで起きていたCCXまたぎによるパフォーマンス低下が心配されそうですが、このあたりはコア間通信レイテンシーの削減や、キャッシュを大量に要求するゲームなどの用途では3D V-Cacheを使ってカバーすることが考えられます。どちらにしても、色々と変わるようですので、どのようなアーキテクチャーやパフォーマンスになるのか気になるところです。