現在主流の半導体製造プロセスは5nmで、今後3nmや2nmでの製造に向けて各社研究開発を勧めていますがTSMCの3nmプロセスにおいてCPUやGPUに重要なSRAMのサイズ縮小が非常に小さい事が明らかになりました。

キャッシュに使われるSRAMのサイズは3nmでも縮小できず。キャッシュ容量はコスト要因に

半導体に関しては毎年、製造プロセスが微細化されることで性能が上がりつつも消費電力や半導体自体のサイズは小さくなるというのを繰り返してきています。これにより、数年前までのハイエンドデスクトップPC並の性能をノートPCでも実現することを可能としていましたが、第68回IEDMにてTSMCが開発の3nmプロセスにおいて衝撃的な情報が出現したようです。

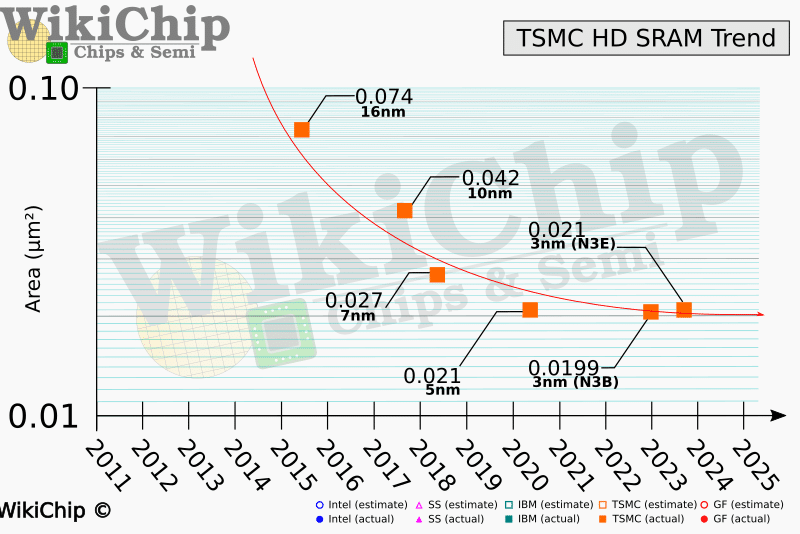

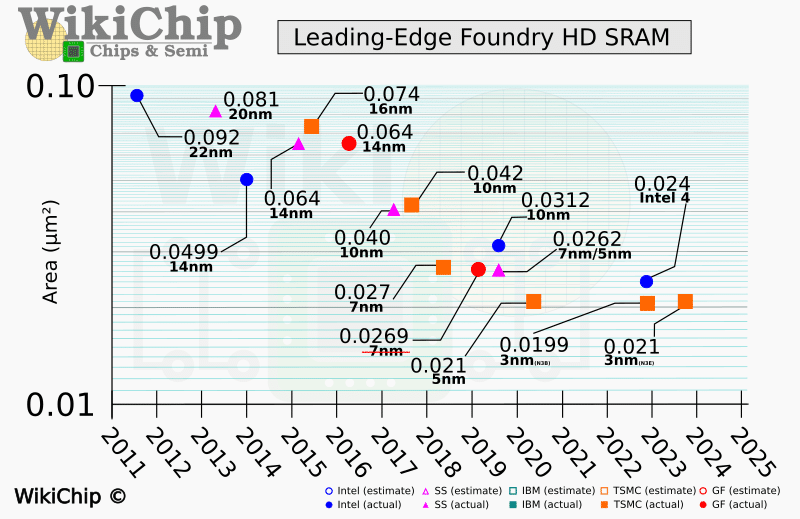

TSMCによるとCPUやGPUのキャッシュに用いられているSRAMについて、TSMCが開発中の3nm(N3BとN3E)では前世代の5nmに対してほとんどサイズ縮小ができていないことが明らかになりました。

TSMCでは5nmに比べるN3BとN3Eについては1.6倍から1.7倍のトランジスター密度を持つようになる一方で、SRAMの密度については1から1.05倍と密度の差が大きくなっています。

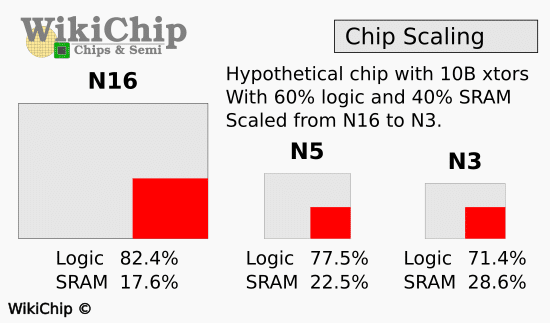

これを例えば100億トランジスターを持つチップで60%がロジック、40%がSRAMとして設計した場合、16nmでは82.4%がロジック、17.6%がSRAMとなりますが、5nmではSRAMが22.5%、3nmではSRAMが28.6%とSRAM密度の向上が止まってしまっているため、同じ容量を実現しようとすると、製造プロセスが進むほどSRAMが占める面積が大きくなってしまうようです。

他社のSRAMの密度に関してはIntelは10nmからからIntel 4 (7nm)に進む際にSRAM密度を1.3倍にしていますが、密度についてはTSMCには敵わず恐らくIntelが3nmなど更なるプロセス微細化を行った際にTSMCを超える事は困難と見られています。

3nmを採用する製品のコストは大幅上昇する可能性。

SRAMに関しては近年重要性が増しており複雑な処理を行う際に重要視されています。CPUではRyzen 9 7950Xには合計81MBのキャッシュが、NVIDIAのGeForce RTX 4090に搭載されているAD102 GPUでは123MBのSRAMキャッシュが搭載されています。

今後、将来的に登場する製品においてもキャッシュ容量は増える見込みなのですが、TSMC 3nmではSRAMが占めるダイ面積を減らす事はできず、現行の5nmと比べてコスト高を緩和する事は困難になると見られています。

この傾向は特に高性能なキャッシュを搭載するハイエンドなCPUやGPUにおいて顕著と言え、将来的に登場するハイエンドモデルのCPUやGPUの価格は現在よりも更に上がる可能性がありそうです。

TSMCはこの問題を認識しているようで、SRAMのサイズをより縮小するN3Sプロセスの投入を検討しているようですが2024年に製造開始するためAMDやApple、NVIDIAの次世代製品に間に合うかは未知数と言えます。

ちなみに、AMDではこの問題を認識していたのかRDNA 3からはチップレットを採用し、大容量SRAMキャッシュであるInfinity Cacheは6nmで製造し、キャッシュ関係が少ないGPU本体部分は5nmで製造しコストを抑えつつ性能を上げていますが、RDNA 4などTSMC 3nmや更にその先のプロセスを使う場合にはこの方法は更に有効と言えそうです。

コメント